Главная функция центрального ядра процессора – управление процессом выполнения программ. Для этого центральный процессор должен иметь непосредственный доступ к памяти, должен быть способен производить все виды вычислений и выполнять запросы на прерывания.

Рассмотрим общие вопросы архитектуры AVR.

Кратка характеристика архитектуры

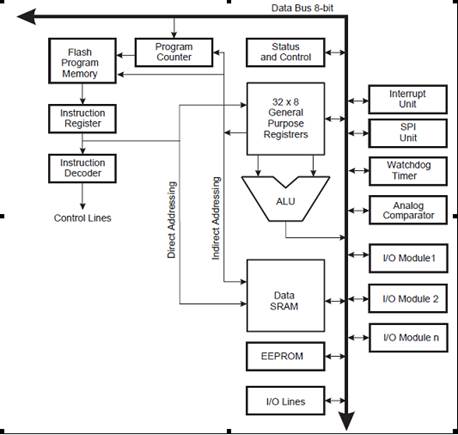

Чтобы максимально ускорить работу и сделать возможным параллельное выполнение нескольких операций, микроконтроллеры AVR используют Гавардскую архитектуру (рис. 3).

Рис. 3 - Блок-схема архитектуры AVR

Такая архитектура предусматривает отдельную память и отдельную шину адреса как для программы, так и для данных.

Каждая команда из пяти программ выполняются за один машинный цикл с использованием многоуровневой конвейерной обработки. В тот момент, когда очередная команда выполняется, следующая команда считывается из программной памяти. Такая концепция позволяет выполнять по одной команде за один такт системного генератора. Программный сегмент памяти физически представляет собой встроенную перепрограммируемую Flash-память.

Файл регистров быстрого доступа содержит 32 восьмиразрядных регистра общего назначения, доступ к которым осуществляется за один такт системного генератора. Это позволяет арифметико-логическому устройству (ОЛУ) осуществлять большинство своих операций за один такт.

Типичная операция АЛУ выполняется следующим образом: из регистрового файла читаются два операнда, выполняется операция. Результат сохранения опять же в файле регистров. Все эти три действия выполняются за один цикл тактового генератора.

Шесть из этих 32 регистраторов могут использоваться как три 16-разрядных регистра-указателя косвенной адресации. Эти сдвоенные регистры могут использоваться для адресации данных в адресном пространстве ОЗУ. Такая организация даёт возможность программного вычисления адреса.

Один из этих регистров-указателей может также использоваться в качестве указателя адреса данных, размещённых в памяти программ (Flash-памяти). Эти дополнительные составные 16-разрядные регистры именуются X, Yи Z.

АЛУ поддерживает арифметические и логические операции между двумя регистраторами или между константой и регистратором. В АЛУ также могут выполняться операции с отдельными регистраторами. После каждой арифметической операции обновляется регистр статуса для того, чтобы отразить информацию о её результате.

Последовательность выполнения программы может быть изменена командами условного и безусловного перехода, а также командой вызова подпрограммы, в которых используется непосредственная адресация.

Большинство инструкций AVRпредставляет собой одно 16-разрядное слово. Каждый адрес памяти программы содержит 16-битовую инструкцию или половину 32-разрядной инструкции.

При выполнении процедуры обработки прерывания или подпрограммы текущее значение счётчика команд (PC)сохраняется в стеке.

Стек фактически размещён в одном адресном пространстве с памятью данных SRAM (ОЗУ) и, следовательно, размер стека ограничен только размером SRAM и тем, какую часть SRAM использует остальная программа.

Программа пользователя обязательно должна инициализировать указатель стека (SP)сразу после сброса (прежде, чем будет выполнена подпрограмма или будет вызвано прерывание). Указатель стека (SP) имеет свой конкретный адрес в пространстве регистров ввода-вывода. К данным в ОЗУ (SRAM) можно получить доступ, используя память различных способов адресации, поддержанных архитектурой AVR.

Адресное пространство всех видов памяти в архитектуре AVR являются регулярным линейным. Гибкий модуль прерываний имеет ряд регистраторов управления в адресном пространстве регистров ввода-вывода и дополнительный флаг глобального разрешения прерываний в регистре статуса.

Каждый вид прерывания имеет свой отдельный вектор в таблице векторов прерываний. Прерывания имеют приоритет в соответствии с их положением в таблице векторов прерываний. Чем ниже адрес вектора прерывания, тем выше приоритет.

Пространство регистров ввода-вывода содержит 64 адреса для регистров управления периферийными устройствами, регистров управления режимами работы процессора и другими функциями ввода/вывода. К любому регистру ввода-вывода можно получить доступ непосредственно по его номеру или как к ячейке памяти данных. В адресном пространстве памяти данных регистры ввода-вывода располагаются сразу после файла регистров общего назначения (0x20 – 0x5F).

Другое по теме:

Элементы систем регулирования цифровых радиопередатчиков Радиопередающие устройства (РПдУ) применяются в сферах телекоммуникации, телевизионного и радиовещания, радиолокации, радионавигации. Стремительное развитие микроэлектроники, аналоговой и цифровой микросхемотехники, микропроцессорной и компьютер ...