Основа модуля – восьмиразрядный компаратор, который непрерывно сравнивает содержимое регистра TCNT0 с содержимым каждого из двух регистров совпадения (OCR0Aили OCR0B). Каждый раз, когда содержимое TCNT0 оказывается равным содержимому OCR0Aили OCR0B, компаратор вырабатывает сигнал совпадения. Этот сигнал устанавливает соответствующий флаг совпадения (OCF0Aили OCF0B) в следующем тактовом цикле.

Если соответствующее прерывание разрешено, установка флага совпадения вызывает прерывание. Флаг совпадения автоматически сбрасывается при запуске процедуры обработки прерывания. Флаг также может быть очищен программно путём записи в него логической единицы.

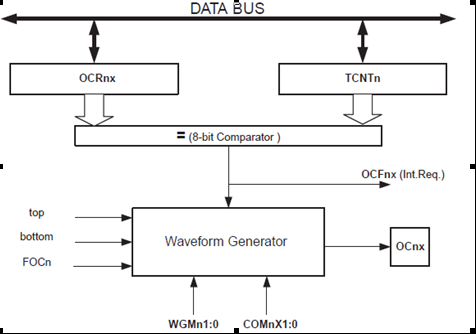

В режиме генератора частот сигнал совпадения используется для генерации выводного сигнала совпадения используется для генерации выводного сигнала в соответствии с выбранным режимом работы, который определяется битами WGM02:0, а также битами выбора режима сравнения (COM0x 1:0). Сигналы max и bottom используются генератором частот в некоторых случаях для получения критических значений в отдельных режимах работы. На рис. 11 показана блок-схема модуля совпадения. На рисунке буква x – это условное обозначение. Для разных модулей совпадения x равно либо A либо B.

Рис. 11 - Блок-схема модуля совпадения

Регистры OCR0xимеют двойную буферизацию в любом режиме широтно-импульсной модуляции (ШИМ). В режиме Normal и режиме СТС (Сброс при совпадении) двойная буферизация отключается. Двойная буферизация синхронизирует момент обновления регистра OCR0xс моментом достижения таймером верхнего или нижнего пределов. Синхронизация предотвращает возникновение ассиметричных ШИМ-импульсов, то есть импульсов, длина которых равна нечётному количеству тактов. Таким образом обеспечивается высокое качество сигналов ШИМ.

Доступ к регистру OCR0xможет показаться слишком сложным. На самом деле это не так. Если двойная буферизация разрешена, центральный процессор обращается к регистрам OCR0xчерез буфер. Если буферизация отключена, центральный процессор обращается к регистрам OCR0xнепосредственно.

Принудительное изменение состояния выхода совпадения

Во всех не-ШИМ-режимах таймера сигнал на любом из выходов совпадения может быть изменён принудительно путём записи единицы в специальный бит FOC0x. Принудительное изменение выхода совпадения не устанавливает флаг OCF0xи не перезагружает таймер.

Сигнал на выходе OC0xбудет изменяться таким же образом, как при реальном совпадении. То есть поведение выхода OC0xбудет зависеть от установки битов COM0x1:0. В зависимости от значения этих битов сигнал на выходе будет либо установлен в единицу, либо сброшен в ноль, либо изменит своё значение на противоположное.

Блокировка режима совпадения в момент записи регистра TCNT0

При записи значения в регистр TCNT0 операция сравнения блокируется в течение одного такта входного сигнала таймера. Это происходит даже в том случае, если таймер остановлен. Эта особенность позволяет записывать в регистр OCR0x то же самое значение, что и в регистр TCNT0, не вызывая прерывания при поступлении на вход таймера/счётчика тактового сигнала.

Другое по теме:

Спроектировать двенадцатипульсный составной управляемый выпрямитель с параллельным включением вентилей Цель данной курсовой работы — спроектировать управляемый выпрямитель и систему импульсно-фазового управления для него. Выпрямитель — устройство, преобразующее переменный ток в постоянный. Он состоит из трансформатора, преобразующего напряжение ...