Пример 5 Преобразование информации из цифровой формы в аналоговую осуществляется с помощью подключения интегральных микросхем цифроаналогового преобразователя (ЦАП) к одному из портов MCS-51. Выдача информации при этом осуществляется с помощью одной команды, например: MOV P1, А.

Если необходимо генерировать какую-то сложную функцию, то лучше записать ее таблично и передавать с соответствующим периодом в заданный порт.

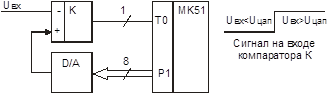

Пример 58. Аналого-цифровой преобразователь (АЦП) последовательного приближения (рис. 10).

Рисунок 10 – Реализация АЦП последовательного приближения

МК выдает через порт P1 байт данных, что превращается в аналоговую форму и сравнивается с входным сигналом компаратора, после чего анализируется результат сравнения. В зависимости от значения сигнала на входе Т0 MCS-51 или оставляет старший бит в единичном состоянии, или сбрасывает в 0. Потом аналогично проверяются все остальные биты.

R4 – регистр цифрового эквивалента;

R3 – регистр бегущего значения 1 для указания весового бита.

CONVRT: MOV R5#08Н ; загрузка счетчика циклов

MOV R3,#01Н

MOV R4,#00Н

LOOP: MOV А, R3 ; сдвиг R3 вправо на 1 разряд

RR A

MOV R3, А

ORL А, R4 ; логическое ИЛИ весового разряда и цифрового эквивалента

MOV Р1, А ; выдача в Р1

JBC T0, ENDUGH; если Т0=1, то аналоговый эквивалент выданного байта больше чем UBX и сохраняется в R4, если наоборот, то установленный бит запоминается в R4

MOV R4, А

ENDUGH: DJNZ R5, LOOP; декремент R5 и если не 0, то переход к анализу следующего бита

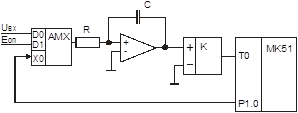

Пример 59. Реализация АЦП методом двойного интегрирования.

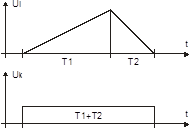

Метод двойного интегрирования заключается в следующем (рис. 11). Сначала интегрируется входной опорный сигнал ЕОП. На выходе интегратора устанавливается отрицательный потенциал, после чего интегрируется входной аналоговый сигнал за строго определенное время Т1. Т1 отсчитывается от момента перехода сигнала интегратора через 0. Потом подается UОП и измеряется время интегрирования Т2, которое пропорционально входному сигналу.

Рисунок 11 – Реализация АЦП двойного интегрирования

Максимальное время преобразования для точности 16 разрядов 2´65.536 мс. Если необходима точность преобразования 8 разрядов, то Т/С0 переключается в режим 8-битного таймера, а время преобразования составляет 2´256 мкс.

Рисунок 12 – Временные диаграммы сигналов АЦП двойного интегрирования

MOV TMOD,#01H; настройка Т/С0 на режим 16 бит

MOV TH0,#HIGH (NOT(T1)+1); загрузка Т/С0

MOV TL0,#LOW (NOT(T1)+1)

SETB P1.1 ; настройка Р1.1 на ввод

SETB Pl.0 ; подача ЕОП на интегратор

WAIT: JB P1.1, WAIT; ожидание появления на выходе интегратора отрицательного уровня сигнала

CLR P1.0 ; подача UBX на интегратор

WAITT0: JNB P1.1, WAIT0; ожидание момента Т0

SETB TCON.4 ; запуск Т/С0

WAITT1: JNB TCON5, WAITT1; ожидание момента Т1

SETB P1.0 ; подача ЕОП на интегратор и начало обратного интегрирования

WAITT2: JB P1,1, WAITT2; ожидание момента Т2

CLR TCON.4 ; остановка Т/С0

CLR TCON.5 ; сброс флажка TF0

MOV В, TH0 ; формирование результата в регистровой паре А, В

MOV A, TL0

Другое по теме:

Синтез системы автоматического регулирования фокусировки пятна В настоящее время оптические дисковые системы нашли множество применений. Возможность записи значительного объема информации и простота тиражирования делает оптический диск очень привлекательным. В сфере записи и хранения данных системы с прямой ...