Разработка арифметико-логического устройства, выполняющего операцию сложения и вычитания в прямом двоичном коде.

Исходные данные:

– разрядность операндов – 8 бит;

– разрядность результата – 8 бит;

– элемент памяти – ПЗУ;

– формат операндов и результата – 8 бит;

Разработка алгоритма устройства

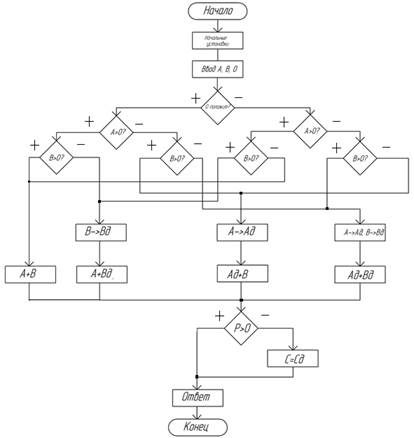

Построим алгоритм заданного логического устройства. Распишем все возможные комбинации сочетания знаков чисел, поступающих на вход устройства с учетом типа операции

1.A+B

2.А+(-В)

3.-А+В

4.-А+(-В)

5.А-В

6.А – (-В)

7.-А-В

8.-А – (-В)

Учтя особенности сложения и вычитания в двоичном коде, получим:

1. А+В

2. А+Вд

3. Ад+В

4. Ад+Вд

5. А+Вд

6. А+В

7. Ад+Вд

8. Ад+В, где д – означает число, переведенное в дополнительный код.

Очевидно, что мы получили пары одинаковых комбинаций. Объединив номера 1 и 6, 2 и 5, 3 и 8, 4 и 7 получим:

1. А+В

2. А+Вд

3. Ад+В

4. Ад+Вд

Теперь мы имеем все данные для построения алгоритма, построим его:

Рисунок 3.2.1. Алгоритм арифметико-логического устройства

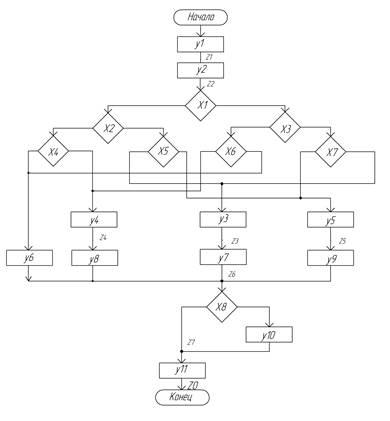

Далее разметим алгоритм с учётом входных, выходных сигналов и состояний для построения абстрактного автомата Мили:

Рисунок 3.2.2 – Алгоритм с учётом входных, выходных сигналов и состояний

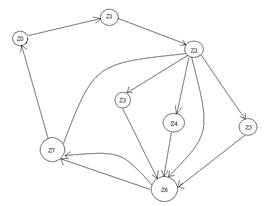

Нарисуем Граф автомата Мили

Запишем составляющие К1, К2, К3, К4, К5

К1=![]()

К2=![]()

К3=![]()

К4=![]()

К5=![]()

Входные сигналы К1, К2, К3, К4, К5, X8, ![]()

По размеченному алгоритму построим таблицу переходов-выходов автомата Мили.

Таблица 3.2 – Таблица переходов-выходов автомата Мили

| 1 |

|

|

|

|

|

|

| |

| Z0 |

| |||||||

| Z1 |

| |||||||

| Z2 |

|

|

|

|

| |||

| Z3 |

| |||||||

| Z4 |

| |||||||

| Z5 |

| |||||||

| Z6 |

|

| ||||||

| Z7 |

|

Другое по теме:

Разработка локальной вычислительной сети (ЛВС) коммерческой организации Причиной создания локальной сети на данной коммерческой организации является: - Совместная обработка информации; - Совместное использование файлов; - Контроль за доступам к важным документам; Актуальность выполнения данной работы заклю ...