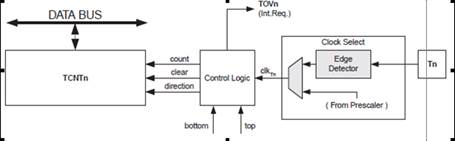

Основой восьмиразрядного таймера/счётчика является программируемый реверсивный счётный модуль. На рис. 10 показана блок-схема счётного модуля и его управляющие сигналы.

Рис. 10 - Блок-схема счётного модуля

Рассмотрим внутренние сигналы:

♦ count – увеличивает или уменьшает содержимое TCNT0 на 1;

♦ direction – выбор между уменьшением и увеличением;

♦ clear – очистка TCNT0 (установка всех битов в ноль);

♦ clkT0 – тактовая частота таймера/счётчика;

♦ top – возникает при достижении TCNT0 максимального значения;

♦ bottom – возникает при достижении TCNT0 минимального значения (нуля).

В зависимости от режима работы таймера, каждый импульс тактового сигнала (clkT0) очищает, увеличивает или уменьшает значение счётчика. Сигнал clkT0может быть получен как от внешнего, так и от внутреннего источника тактового сигнала. Это определяется битами выбора тактового сигнала (CS02:0). Когда не выбран ни один источник тактового сигнала (CS02:0 = 0), таймер останавливается.

Центральный процессор может обращаться к значению регистра TCNT0 независимо от того, присутствует ли сигнал clkT0 или нет. Команда записи, поступающая от центрального процессора, имеет приоритет над всеми другими операциями (очистки счётчика или операциями счёта).

Режимы работы таймера определяются установкой битов WGM01 и WGM00 регистра TCCR0Aи битом WGM02 регистра TCCR0B. Есть тесная связь между выбранным режимом работы счётчика и частотой сигнала на выходе OC0A.

Флаг переполнения таймера/счётчика (TOV0) устанавливается в соответствии с режимом работы, выбранным при помощи битов WGM01:0. Флаг TOV0 может использоваться для генерации прерываний центрального процессора.

Другое по теме:

Система автоматического регулирования фокусировки пятна В настоящее время оптические дисковые системы нашли множество применений. Возможность записи значительного объема информации и простота тиражирования делает оптический диск очень привлекательным. В сфере записи и хранения данных системы с п ...