q Регистр команд (Instruction Register), в котором хранится текущая команда. Разрядность регистра команд должна быть больше или равна 2.

q TAP controller. По сути, это конечный управляющий автомат для тестовой логики.

Как видно из схемы, тестовая логика предоставляет возможность выбирать путь прохождения данных от TDI к TDO: либо через регистр команд (Instruction Register), либо через регистр данных (Data Register). Регистром данных в каждый момент времени может быть один из следующих регистров:

q Последовательный сдвиговый регистр граничного сканирования (Boundary-Scan register).

q Какой-либо внутренний регистр, предусмотренный разработчиком устройства (Internal register).

q Регистр обхода (Bypass register).

q Идентификационный регистр (Identification register).

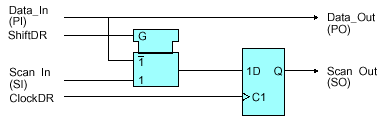

Рассмотрим регистр сканирования. Ячейки граничного сканирования (Boundary-Scan cells) подразделяются на два типа: входные (размещаются на тех первичных входах устройства, где временной фактор критичен – например, на входе синхронизации) и обычные. Схема входной ячейки показана на рис. 5.

Рисунок 5.

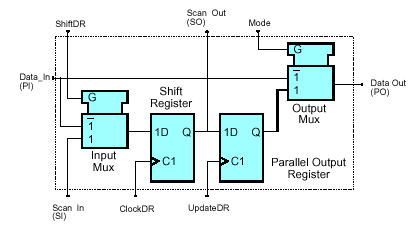

Как видно из этой схемы, сигнал проходит по линии данных без задержек. Однако, там где это возможно на входных линиях, а также на всех выходных линиях располагают обычные ячейки. Структура типичной ячейки граничного сканирования представлена на рис. 6.

Рисунок 6

Рассматриваемая ячейка состоит из двух D-триггеров, работающих по прямому фронту, двух мультиплексоров “2-в-1”, четырех входов и двух выходов. Назначение структурных элементов схемы:

q Data_In и Data_Out – вход и выход (относительно ячейки) линии данных, на которую эта ячейка и помещена. (PI – parallel input, PO – parallel output).

q Scan In и Scan Out – соответственно, вход и выход сканируемых данных (SI – serial scan input, SO – serial scan output). Т.е. на SI данные приходят с SO предыдущей ячейки (либо с TDI, если это первая ячейка в пути), проходят через первый D-триггер и выходят на SO, чтобы попасть на SI следующей ячейки (или на TDO, если это последняя ячейка в пути).

q ShiftDR – определяет источник информации для первого D-триггера: Data_In (режим Capture) либо Scan In (режим Shift).

q Mode – определяет, что пропускать на линию данных Data_Out: сигнал с Data_In (режим Normal) либо сигнал со второго D-триггера (режим Update).

q ClockDR – синхронизирующий вход первого D-триггера, т.е. для режимов Capture и Shift.

q UpdateDR – синхронизирующий вход второго D-триггера (режим Update)

Ниже приведена таблица режимов функционирования ячейки:

| Режим | ShiftDR | Mode | Функционирование |

| NORMAL | - | 0 | PI ® PO |

| CAPTURE | 0 | - | PI ® SO по фронту на ClockDR |

| SHIFT | 1 | - | SI ® SO по фронту на ClockDR |

| UPDATE | - | 1 | SO ® PO по фронту на UpdateDR |

Другое по теме:

Суммирующий счетчик 1) Используя параметры эквивалентного логического элемента, разработанного в предыдущем КП по курсу «Компьютерное моделирование интегральных приборов», спроектировать схему триггера с динамическим управлением (фронтом или срезом синхросигнала) в ...