Как видно из структуры ячейки, путь сканирования TDI ® SI1 ® SO1 ® ¼® SOi-1 ® SIi ® SOi ® SIi+1 ® ¼ ® TDO физически не пересекается с линиями данных PI®PO ячеек граничного сканирования. Таким образом, регистр граничного сканирования является “прозрачным” для самого устройства. Для осуществления операций сканирования отсутствует необходимость переключаться в специальный тестовый режим. Влияние тестовой логики на функционирование устройства сведено к минимуму. На входных линиях задержка прохождения сигнала может отсутствовать вообще, а на выходных – равна задержке выходного мультиплексора (Output Mux).

Внутренний регистр (Internal register), предусмотренный разработчиком устройства, например, для хранения результирующей сигнатуры проверки устройства, если в нем реализованы средства встроенного самотестирования.

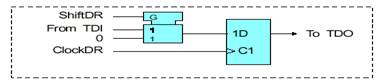

Регистр обхода (Bypass register) – простой, но очень важный элемент в рассматриваемой архитектуре. Он создает кратчайший путь между TDI и TDO, не затрагивая при этом все остальные регистры. Необходимость такого регистра обусловлена ранее оговоренной возможностью соединения нескольких устройств в последовательный путь сканирования. Если нам необходимо иметь доступ не ко всем, а только к некоторым устройствам в цепочке, то остальные устройства устанавливаются в режим Bypass, образуя минимальные задержки прохождения сканируемых данных. Bypass register состоит из одного мультиплексора “2 в 1” и одного D-триггера, синхронизированного прямым фронтом (рис. 7). Отсутствует параллельный вывод данных (в связи с чем, сигнал Update_DR отсутствует в схеме), но есть некоторая особенность с операцией Capture – в регистр может записываться аппаратно реализованное значение 0 (т.е. производится захват значения 0).

Рисунок 7

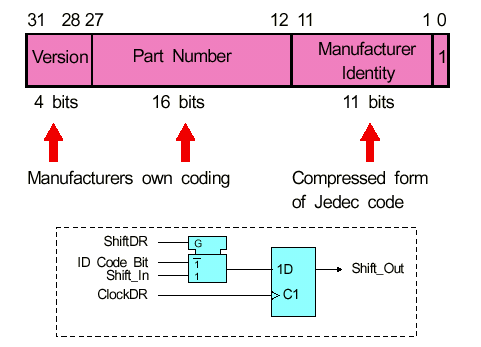

Регистр Идентификации (Identification register) – необязательный 32-битый регистр с режимами сбора данных и сдвига (рис. 8). 32 бита идентифицируют устройство через следующие поля:

–Бит 0 (младший разряд) всегда равен 1.

–Биты 1 – 11 идентифицируют фирму-изготовителя устройства. Используется краткая форма кода идентификации JEDEC.

–Биты 12 – 27 обеспечивают 16-битное поле свободного формата с серийным номером устройства.

–Биты 28 – 31 обеспечивают 4-битное поле свободного формата, чтобы описать до 16 различных версий того же основного устройства.

Регистр команд (Instruction Register) состоит из собственно сдвигового регистра, некоторой декодирующей логики (в зависимости от количества и типов реализуемых команд) и секции хранения декодированной команды, в которую как только команда поступает, она сразу же поступает на выполнение (рис. 9). Стандарт IEEE 1149.1, во-первых, предписывает, что есть только 3 обязательные команды, необходимые для функционирования аппарата Boundary-Scan, а все остальные являются необязательными (дополнительными), во-вторых, обязательные и дополнительные команды в стандарте только описываются функционально, а их реализация на аппаратном уровне оставлена полностью на усмотрение разработчика. Последнее, кстати, относится ко всему тестовому обрамлению устройства.

Следующие три команды должны обязательно быть реализованы тестовой логикой :

q BYPASS (обход) – команда, устанавливающая Bypass register между TDI и TDO. Код команды – все единицы (число разрядов регистра команд ≥2, поэтому для регистра минимальной длины код команды – 11). Режимы Shift и Capture с «0».

Рисунок 8 Перейти на страницу: 1 2 3 4 5

Другое по теме:

Техника антенных устройств Развитие антенной техники на всем протяжении эволюции радио сопровождалось и было тесно связано с развитием теории антенных устройств. Уже первая работа Генриха Герца по экспериментальному доказательству существования электромагнитных волн была им ...