С середины 70-х годов структурное тестирование печатных плат основывалось на физическом доступе к устройствам и межсоединениям на плате с помощью так называемого «ложа из гвоздей» (рис. 1). С развитием технологии изготовления печатных плат, стали уменьшаться расстояния между соседними медными дорожками – стало более рискованно каждый раз класть плату на гвозди. Появились двухсторонние платы, и инженерам пришлось прикладывать гвозди с двух сторон. Вопрос о физическом доступе был исчерпан с появлением многослойных печатных плат.

Рисунок 1

С такими проблемами столкнулись в середине 80-х большинство производителей. Для поиска возможных решений была создана группа JTAG (Joint Test Action Group), которая с помощью 200 ведущих фирм в течение 5 лет разработала стандарт Boundary-Scan IEEE 1149.1 (IEEE – Institute of Electrical and Electronic Engineers).

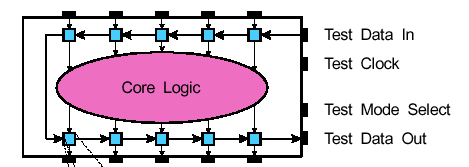

В основу принципа была положена концепция размещения последовательного сдвигового регистра по границам устройства (рис. 2) Причем, сами ячейки такого регистра располагаются непосредственно между первичными входами/выходами устройства и логическим ядром.

Рисунок 2

Таким образом, в устройство добавляется 4 контакта: TDI (Test Data In – вход тестовых данных), TDO (Test Data Out – выход тестовых данных), TMS (Test Mode Select – выбор тестового режима) и TCK (Test Clock – тестовая синхронизация).

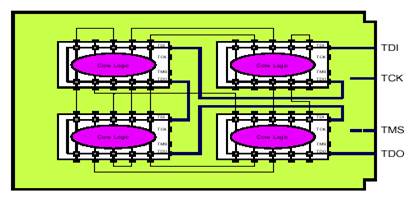

Рисунок 3.

Сущность механизма сканирования сходна с методом Scan Path. Однако, есть существенные различия. Во-первых, логика ядра может быть любой, в том числе содержать последовательностные структуры (не нужно разбивать устройство на комбинационную часть и память). Во-вторых, ячейки сканирования располагаются как до, так и после логики.

Несколько устройств на плате могут быть объединены в единый последовательный путь сканирования (рис. 3). Это можно сделать путем соединения TDO с TDI следующего устройства. Таким образом, на плате появляется также 4 дополнительных вывода: TDI и TDO, и общие для всех устройств TCK и TMS.

Таким образом, технология граничного сканирования при относительно небольших аппаратурных затратах позволила реализовать нечто вроде «виртуальных гвоздей», что обеспечивает не только 100% наблюдаемость, но и 100% управляемость входов/выходов устройств.

Несомненно, технология Boundary-Scan является значительным прорывом вперед в DFT. Рассмотрим архитектуру устройства, которую описывает стандарт IEEE 1149.1.

Общая схема устройства представлена на рис. 4.

Рисунок 4.

Само устройство, реализующее требуемые функции (которое, как мы видим, может содержать и некие внутренние регистры), помещается в обрамление из тестовой логики, которое составляют:

q Набор из 4 обязательных тестовых ножек: TDI, TDO, TMS и TCK. Также возможно добавление еще одной необязательной тестовой ножки – TR (Test Reset – сброс тестовой логики). Все вместе они называются TAP (Test Access Port – тестовый порт доступа).

q Ячейки граничного сканирования на каждой линии первичного входа или выхода, соединенные между собой, таким образом, чтобы организовать последовательный сдвиговый регистр.

q Однобитный регистр обхода (Bypass register).

q Необязательный 32-битный идентификационный регистр, с возможностью хранения в нем неизменяемого кода устройства. Перейти на страницу: 1 2 3 4 5

Другое по теме:

Расчет антенны со смещенным рефлектором Зеркальные антенны - наиболее распространенный тип остронаправленных СВЧ антенн в радиолокации, космической радиосвязи и радиоастрономии. В процессе проектирования необходимо определить размеры зеркала, распределение поля в раскрыве антен ...